Actel ProASIC3

FPGA (Field Programmable Gate Array) je zajímavá moderní elektronická součástka. Dala by se přirovnat k nepájivému kontaktnímu poli s mnoha drátky a propojkami, a to vše je na jednom čipu. Dnes se podíváme na jeden takový obvod od firmy Actel.

- Úvod

- Actel ProASIC3

- Zdroje informací

1. Úvod

Rozdělení programovatelných obvodů

- 1.1. Klasické PLD

- 1.2. Komplexní PLD

- 1.3. FPGA

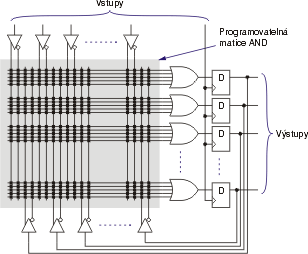

1.1. Klasické PLD

(Programmable Logical Device)

PAL, GAL a PALCE; PLA

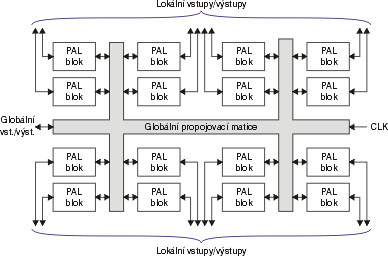

1.2. Komplexní PLD (CPLD)

1.3. FPGA - Field Programmable Gate Array

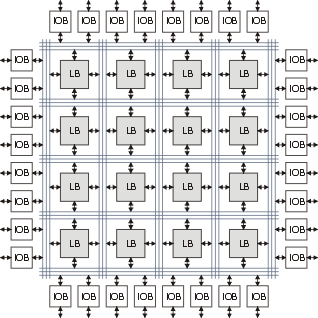

Typická struktura FPGA:

IOB = Input/Output Block

LB = Logic Block

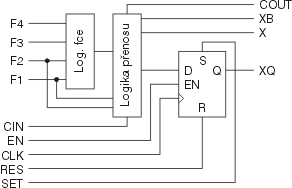

Typická struktura LB:

Field i Array znamenají v češtině pole. Jak se to tedy dá přeložit?

„Na poli“ programovatelné hradlové pole

„Pole“ běžného světa versus extrémně sterilní prostředí při výrobě křemíku.

2. Actel ProASIC3

Zajímavá zpráva:

FPGA ProASIC3 od Actelu byla vybrána pro miniaturní zařízení pro testování a měření založené na USB komunikaci.

Zařízení s pamětí Flash vyhověla požadavkům společnosti Elan Digital Systems na cenu, velikost, bezpečnost, výkon a provedení.

(24.4.2006)

„Bezpečnostní hledisko tohoto FPGA bylo z velké části rozhodující, abychom naše zařízení USBScope50 (podrobný popis) mohli dodat na trh,“ říká ředitel společnosti Elan.

Co to je ProASIC3?

ASIC (Application Specific Integrated Circuit) Označení integrovaného obvodu (nebo obvodů), který je vytvářen jako jednoúčelový na zakázku, obvykle v menších množstvích. Kvůli úspoře návrhu a výrobního procesu se obvykle vychází z rozsáhlejšímo modelu čipu, který je jednoduše upraven nebo omezen tak, aby plnil zákaznický účel.

ASIC = zákaznický obvod

ProASIC = 1. generace nízkopříkonový, nonvolatilní, reprogramovatelný

ProASICPLUS = 2. generace FlashLock, Live at Power Up

ProASIC3/E = 3. generace obvodu vylepšeno zabezpečení, možnost implementace jádra ARM7, nízká cena

Základní charakteristika

První FPGA s uživatelsky využitelnou pamětí Flash přímo na čipu: 1 kbit.

30 k – 3 M hradel.

71 – 616 vstupně – výstupních vývodů podle typu pouzdra.

Až 504 kbit dual-port RAM (paměť se současným dvojím přístupem).

Až 6 jednotek PLL: pro časování různých částí obvodu.

Možnost implementace jádra ARM7

Zabezpečení proti zcizení intelektuálního vlastnictví (softwaru) pomocí 128-bitového kódovacího algoritmu.

Nízká cena a dostupnost

Údajně nejlevnější FPGA na světě.

Od $1.50 za kus při odběru 250 000 ks.

7 typů součástek lze koupit za méně než $10 za kus při odběru 250 000 ks.

Na našem trhu není běžně k sehnání.

Přesné ceny nelze najít na stránkách výrobce ani distributorů. Hodně záleží na odebíraném množství.

Vysoký výkon

Taktovací frekvence: až 350 MHz

Využití až 95% logiky

Možnost komunikace po 64-bit PCI sběrnici při 66 MHz a 3,3 V.

Napěťové úrovně

Jádro je napájeno 1,5 V.

Přepínatelné úrovně pro vstupně-výstupní logiku: 1,5 V, 1,8 V, 2,5 V, 3,3 V.

Až 8 vstupně-výstupních sekcí; každá sekce může pracovat na jiných napěťových úrovních.

Jeden čip

Nepotřebuje další obvody pro nahrání konfigurace při zapnutí.

vyšší spolehlivost systému

menší spotřeba místa na desce

nižší celkové náklady

vyšší bezpečnost intelektuálního vlastnictví

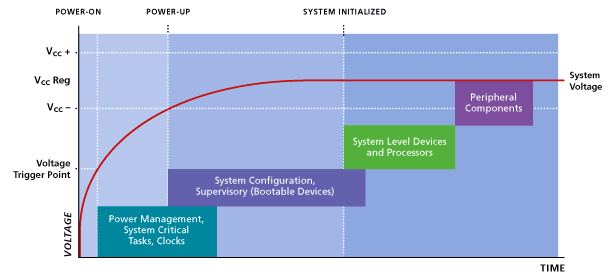

„Live-At-Power-Up“

Inicializace součástky probíhá v několika fázích už při náběhu napájecího napětí.

Odolnost vůči neutronům

Z atmosféry se může do zařízení dostat neutron s vysokou energií. To obvykle u (jiných) zařízení s programem v paměti SRAM vede ke zhroucení systému.

Výrobce zaručuje, že díky programové paměti Flash toto nebezpečí nehrozí. :-)

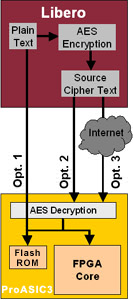

Bezpečné programování na desce (Secure ISP)

Zabudovaný kryptovací algoritmus AES a šifrovací klíč AES-128 (běžně využívaný v průmyslu), uložený v paměti Flash.

Umožňuje bezpečné aktualizace systému pomocí veřejných sítí, např. internet.

Možnosti bezpečného uzamknutí programové paměti

Pomocí klíče, který má 79 až 263 bitů. Stejným klíčem lze paměť odemknout.

Permanentní uzamknutí programové paměti.

FlashLock (viz Opt. 1): pomocí 128-bitového klíče, který je uložen v paměti Flash.

Doplňkový 128-bitový AES dekryptovací klíč (viz Opt. 2): součástka je předprogramována dekryptovacím klíčem. Při finální výrobě je výrobní firmě dodán kryptovaný kód, kterým součástku naprogramuje. Během programování je kód dekryptován.

Vzdálené přeprogramování pomocí internetu („field upgrade“): opět pomocí kryptovacího klíče. Případné zachycení dat během programování nelze zneužít bez znalosti klíče.

Zabezpečená výroba zařízení

Díky kryptovacím algoritmům lze bezpečně celé zařízení předat do výroby třetím stranám bez nebezpečí zcizení intelektuálního vlastnctví nebo úmyslného naprogramování jiným kódem.

Program nemůže být vyčten z paměti, ale může být po naprogramování bezpečně verifikován.

Označování typových řad

A3Pxxx – ProAsic3 s „nízkou“ hustotou hradel

xxx = počet systémových hradel v tisících:

030, 060, 125, 250, 400, 600, 1000A3PExxx – ProAsic3 s „vysokou“ hustotou hradel

xxx = počet systémových hradel v tisících:

600, 1500, 3000M7A3P... – podpora jádra ARM7

Řady A3P a A3PE se částečně vzájemně překrývají. Hlavní rozdíly mezi oběma řadami:

| A3P | A3PE | |

|---|---|---|

| počet jednotek PLL | 0 - 1 | 6 |

| I/O banky (+JTAG) | 2 nebo 4 | 8 |

| pouzdra | 100 – 484 vývodů | 208 – 896 vývodů |

Vstupy / výstupy

700 Mbps DDR

1.5 V, 1.8 V, 2.5 V a 3.3 V logika

Jednoduché (Single-Ended) I/O Standardy: např. LVTTL, LVCMOS, PCI, PCI-X

Differenciální I/O Standardy: např. LVPECL, LVDS, BLVDS, M-LVDS

Programovatelná rychlost přeběhu na výstupu a proudová zatížitelnost

Programovatelné piny pro referenční napětí

Slabé Pull-Up/Down

Rozhraní JTAG (IEEE1149.1 Boundary Scan Test)

Pinově kompatibilní v rámci celé rodiny ProASIC3

Časování

6 časovacích bloků s PLL

Proměnný fázový posun, násobení/dělení frekvence, programovatelné zpoždění

Široký rozsah pracovních frekvencí: 1,5 MHz až 350 MHz

Struktura pamětí

Volitelná struktura paměťových bloků: ×1, ×2, ×4, ×9, ×18

„True Dual-Port“ SRAM

24 konfiguračních možností SRAM a FIFO

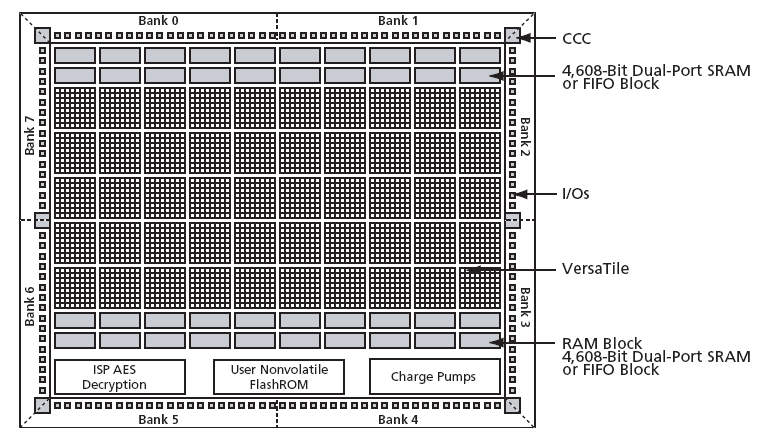

Architektura

FPGA VersaTiles

Paměť Flash ROM – uživatelsky využitelná

Paměť SRAM / FIFO

Obvody pro řízení hodin a PLL

Vstupně-výstupní obvody

Architektura - schéma

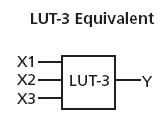

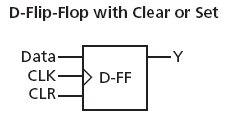

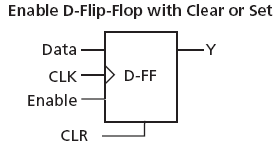

VersaTiles – základní buňka

Lze naprogramovat jako:

Kombinační logika: umožňuje realizovat všechny 3-vstupové logické funkce

Asynchronní registr typu „Latch“ (závora) s nulovacím (Clear) nebo nastavovacím (Set) vstupem

Synchronní registr typu D s nulovacím (Clear) nebo nastavovacím (Set) vstupem

Synchronní registr typu D s nulovacím (Clear) nebo nastavovacím (Set) vstupem a vstupem Enable

Statická paměť RAM (SRAM)

Každý paměťový blok lze nakonfigurovat nezávisle jako 256×18, 512×9, 1k×4, 2k×2 nebo 4k×1 bity.

Paměťový blok může fungovat v režimu FIFO.

Příznaky Almost-Empty a Almost-Full.

Implementace jádra ARM7

Processor rodiny ARM7™ optimalizovaný pro FPGA

Architektura 32/16-Bit RISC

Instrukční sada 32-Bit ARM nebo16-Bit Thumb

32-Bit Unified Bus Interface

3-úrovňový pipelining

32-bitová ALU

32-bitový rozsah adresování paměti

Statický režim

Jednotka JTAG Interface

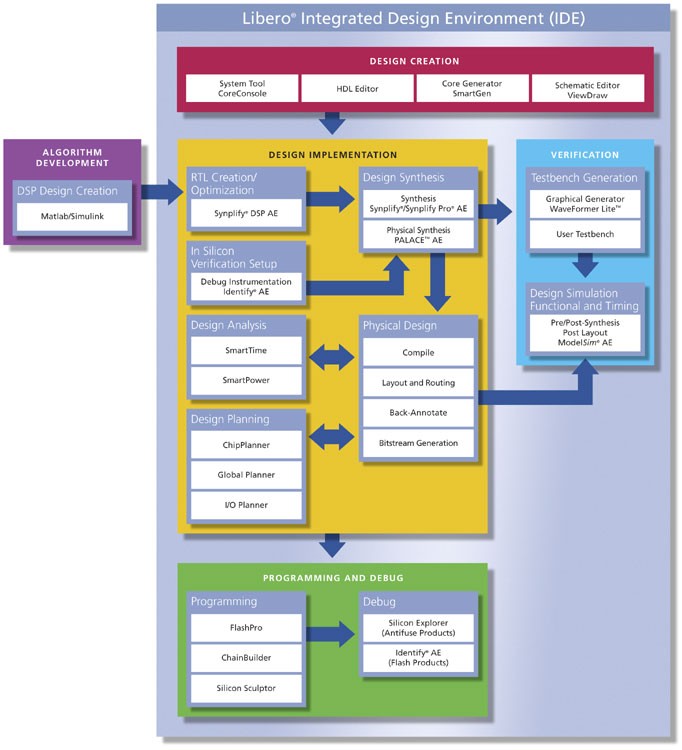

Vývojové prostředí Libero IDE

Možnost stažení omezené verze zdarma po registraci.

Plná verze je funkční 45 dnů.

Platformy: Windows, Solaris a Linux.